450MHzのクロック生成(その1 失敗) (2021年2月12日)

アナログデバイセスのDDSーIC、AD9952のクロックを生成します。

AD9952のクロックは最大400MHzですが、かなりのオーバークロックに

耐え、600MHzぐらいでも大丈夫だそうです。

そこまで無理はせず、450MHzとします。

AD9952には内部にPLL発振回路による逓倍回路があり、

20倍まで逓倍できます。例えば、20MHzをAD9952に加えれば

簡単に内部で400MHzのクロックを生成できます。

しかしながら内部のPLL発振の純度はどうしても悪くなり

結局、出力の純度も低下してしまいます。

純度の高いクロックを外部で生成し、それをAD9952に加えたいと

考えました。

そこで、50MHzの水晶発振出力を9逓倍することにしました。

いきなり9倍の450MHzを得るのは難しいので、まず50MHzを

3逓倍して150MHzを得て、それをさらに3逓倍して450MHzを

得ることにします。

|

|

50MHzの水晶発振器を秋月電子で買いました。

信号純度は-145 dBc/Hz Typ. @1kHz

というものです。

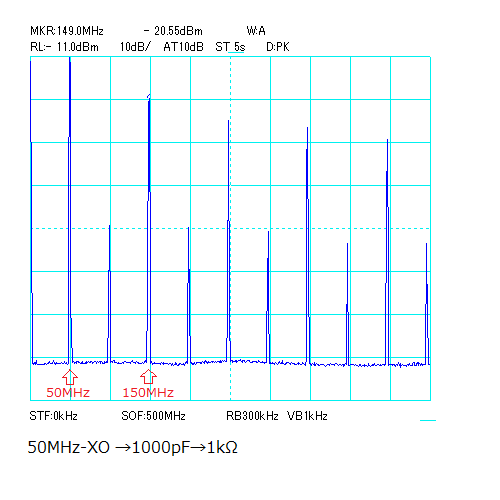

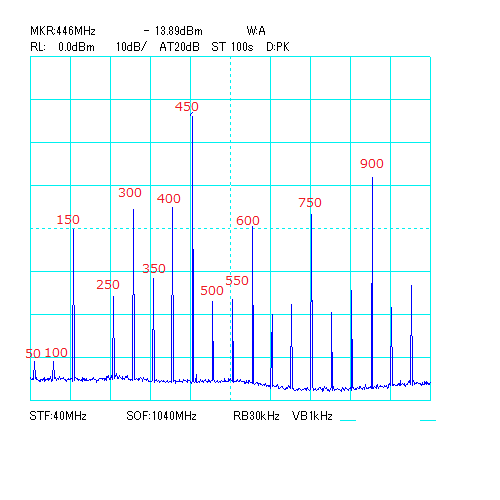

これの出力(3.3V CMOSレベル)を観測しました。

50Ω負荷(スペアナの入力Z)では重過ぎですので、

1000pFで直流カット後、直列に1kΩを入れてから

スペアナで観測しました。

ズラリと50MHzの整数倍成分が並んでいますね。

方形波ですので、奇数倍成分が強いです。

50MHzでは、出力=-11dBmと、当たり前ですが

一番強くて、150MHzは、50MHzよりも10dBほど

低いです。

|

|

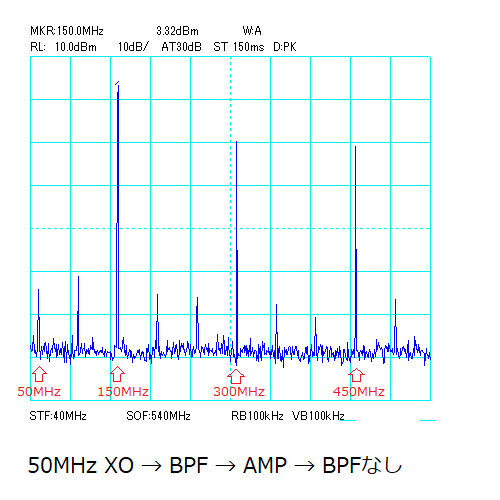

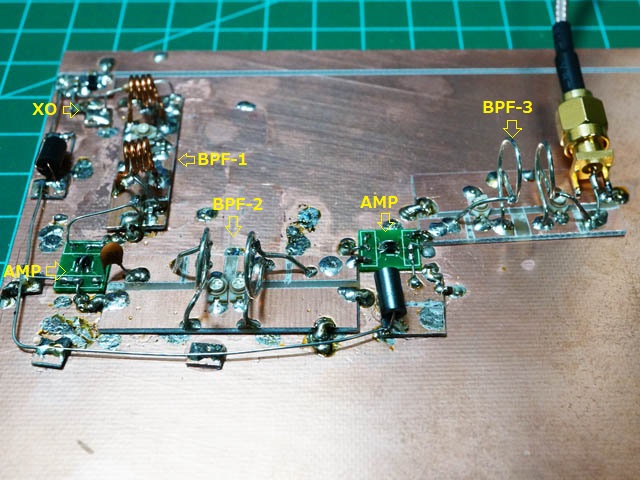

50MHz XOの後ろに150MHzのBPFを入れ、

これまた秋月電子で買ったBGA2800(1個¥15という

格安部品です)という広帯域RFアンプで増幅しました。

|

|

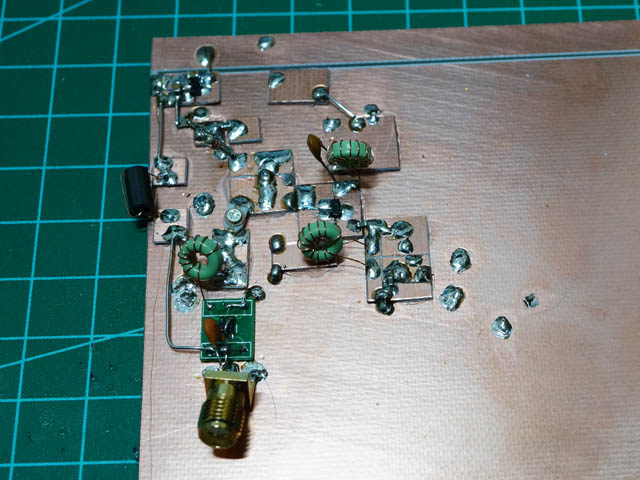

最初はトロイダルコアを使ったBPFでした。

|

|

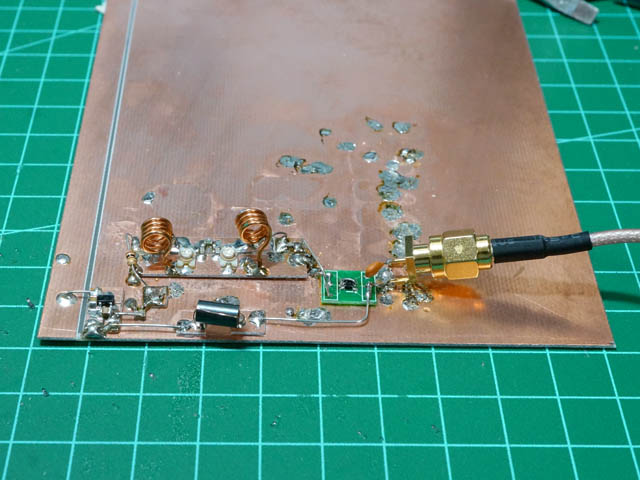

空芯コイルによるBPFの方が良かったです。

|

|

さらにBGA2800によるアンプの後に

450MHzのBPFを入れ、もう一度アンプ、

その後ろに450MHzのBPFを入れました。

|

|

その450MHzの出力ですが、、、

スプリアスだらけですね。

元の50MHzも残り、その整数倍の高調波がたくさん

見えます。

基板貼り付け法で簡単に作ってしまいましたが

これではよろしくありません。

作り直すことにします。

3逓倍した後、徹底的に50MHz、100MHz、200MHz、

250MHz、300MHz、350MHz、400MHzを取り除く

べきです。

もうちょっとしっかりと作らないとダメです。

|

|

|